# Over-60-GHz Design Technology for an SCFL Dynamic Frequency Divider Using InP-Based HEMT's

Yohtaro Umeda, *Member, IEEE*, Kazuo Osafune, *Member, IEEE*, Takatomo Enoki, *Member, IEEE*, Haruki Yokoyama, Yasunobu Ishii, *Member, IEEE*, and Yoshihiro Imamura

**Abstract**—A toggle operation of 39–63.5 GHz without tuning has been achieved by a digital dynamic frequency divider (DFD). The DFD employs a pair of clocked inverters (CI's) with source-coupled FET logic (SCFL) and uses 0.1- $\mu$ m-gate InAlAs/InGaAs/InP high electron-mobility transistors (HEMT's) of good uniformity and high performance. On a 2-in wafer, the frequency divider showed a maximum toggle frequency ( $f_{\text{tog, max}}$ ) of  $59.1 \pm 3.3$  GHz and a fabrication yield of 89%. This is the highest operation frequency ever reported for a broad-band digital frequency divider. Comparison of the DFD and the static frequency divider (SFD) showed that the ratio of  $f_{\text{tog, max}}$  for the DFD to that for the SFD is much higher than the value expected from the linear-response theory. The comparison also showed that the ratio of the measured  $f_{\text{tog, max}}$  for the DFD to that for the SFD is 1.7, in contrast with the value of two expected from the circuit simulation. Delay-time analysis revealed that this 15% decrease of the ratio is due to the transmission delay of interconnections and charging time for stray capacitance.

**Index Terms**—Frequency conversion, digital integrated circuits, indium compounds, MODFET integrated circuits.

## I. INTRODUCTION

THE InAlAs/InGaAs/InP high electron-mobility transistors (HEMT's) have demonstrated excellent ultrahigh-frequency [1], [2] and low-noise [3] performance and have been used in various monolithic microwave integrated circuits (MMIC's) for the millimeter-wave band, such as low-noise amplifiers [4], [5], high-power amplifiers [6], traveling-wave amplifiers [7], mixers [8], and oscillators [9]. They have also been used in the integration of these kinds of millimeter-wave circuits [10]. Although they have been used in a few digital integrated circuits (IC's) (i.e., 26.7-GHz frequency divider [11]), there have been few such applications because of the difficulty of attaining the larger scale integration which is more common in digital IC's than in MMIC's. Using an electron beam (EB)/photo hybrid T-shaped-gate process and an InP recess-etch stopper in these types of HEMT's

and using source-coupled FET logic (SCFL) gates [12], we have been able to make a 40.4-GHz static frequency divider (SFD) [13], 46-Gb/s multiplexer [14], and 40-Gb/s demultiplexer [14] for optical transmission systems. However, for emerging frequency-division applications at frequencies far above 40 GHz, dynamic frequency dividers (DFD's) are the only demonstrated devices. Two types of analog DFD's have recently been reported: a 57–64-GHz regenerative DFD IC using GaAs-based HEMT's [15] and a 75-GHz DFD IC with an injection-locked push–pull oscillator using InP-based HEMT's [16]. These types of DFD's are advantageous in ultrafast operation, but their locking range for a fixed bias condition is intrinsically narrow and they need to be tuned if they are to operate over a broad frequency range [16]. In contrast, digital DFD's not only operate at high speeds, but also have a broad-band operation range without tuning. There have, for example, been reports on a 28–51-GHz DFD IC with dual-ring oscillators gated by transfer gates using GaAs-based HEMT's [17] and on a 25–50-GHz DFD IC with a dynamic toggle flip-flop (DTFF) composed of two clocked inverters (CI's) using GaAs-based heterojunction bipolar transistors (HBT's) [18]. We adopted the latter type of digital DFD's because the basic gate of this type of frequency divider is the same as the one for digital circuits such as the dynamic D flip-flop (D-FF) [19]. This type of frequency divider can, therefore, also be considered a benchmark for the operation frequency of ultrahigh-speed digital IC's in dynamic operation.

In this paper, we describe the design and performance of a digital DFD with a pair of SCFL CI's using InAlAs/InGaAs/InP HEMT's. The advantage of CI's in broad-band operation and the good uniformity and high performance of the HEMT's give this frequency divider 63.5-GHz toggle operation and a 24.5-GHz operation bandwidth without tuning. This frequency divider demonstrates the feasibility of digital circuits operating at more than 60 GHz. In addition, comparison of this DFD with the SFD using a static toggle flip-flop (STFF) composed of a pair of D-latches shows that the DFD operates at a speed higher than that predicted from the delay time when using linear response theory. Moreover, a delay-time analysis for the fabricated DFD and SFD shows that interconnections and stray capacitance decrease the speed of IC's, and also shows how to further increase the operation speed of the DFD.

Manuscript received May 30, 1997; revised May 31, 1998.

Y. Umeda, K. Osafune, T. Enoki, H. Yokoyama, and Y. Ishii are with NTT System Electronics Laboratories, Atsugi-shi Kanagawa 243-01, Japan (e-mail: umeda@aecl.ntt.co.jp).

Y. Imamura was with the NTT System Electronics Laboratories, Atsugi-shi, Kanagawa 243-01, Japan. He is now with the Corning Shizuoka Technical Center, Corning Company Ltd., Osuka-cho, Ogasa-gun, Shizuoka 437-1302, Japan.

Publisher Item Identifier S 0018-9480(98)06169-9.

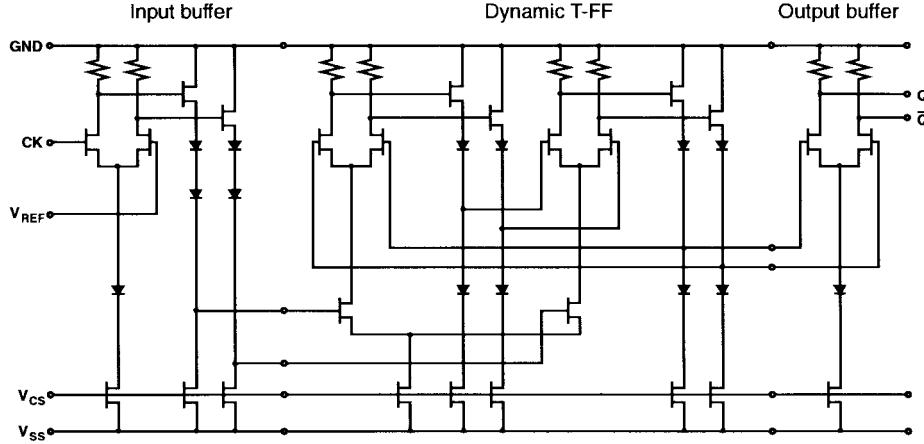

Fig. 1. Circuit diagram of the SCFL DFD using a DTFF composed of two CI's.

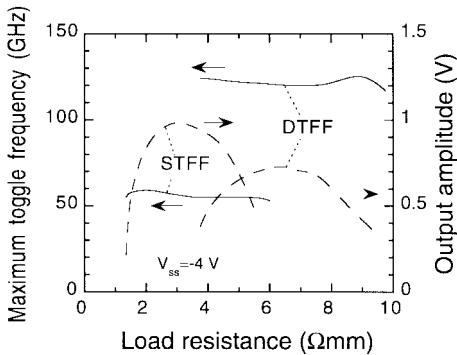

Fig. 2. Calculated dependence of the maximum toggle frequency and the output amplitude of the DTFF and the STFF on the load resistance. The output amplitude is calculated at 120 GHz for the DTFF and 55 GHz for the STFF.

## II. DESIGN

As shown in Fig. 1, the SCFL DFD consists of an input buffer converting a single-ended input signal to a differential signal, DTFF composed of two CI's, and an output buffer driving  $50\text{-}\Omega$  lines. Fig. 2 shows the calculated dependencies (by circuit simulation) of the maximum toggle frequency ( $f_{\text{tog max}}$ ) and the output amplitude ( $V_{\text{out}}$ ) on the load resistance ( $R_L$ ) of the DTFF. The corresponding dependencies are also shown for the STFF using two D-latches [13]. The dependence of  $f_{\text{tog max}}$  on  $R_L$  is weak for both circuits and the ratio of  $f_{\text{tog max}}$  for the DTFF to that for the STFF is about two. Because of the weak dependence of  $f_{\text{tog max}}$  on  $R_L$ , the design focused on stable operation (i.e., large output amplitude) rather than high-speed operation: the designed  $R_L$  values for the DTFF and the STFF were 6.5 and  $2.25\text{ }\Omega\cdot\text{mm}$ , respectively.

The minimum  $R_L$  for toggle operation for the DTFF is approximately  $3.7\text{ }\Omega\cdot\text{mm}$ , whereas the corresponding  $R_L$  for the STFF is  $1.4\text{ }\Omega\cdot\text{mm}$ . This large minimum  $R_L$  for the DTFF is due to the absence of a latching function in the CI. According to linear-response theory as applied to SCFL gates [19], the delay time ( $\tau$ ) for a CI ( $\tau_{\text{CI}}$ ) and a D-latch ( $\tau_{\text{DL}}$ ) can be approximated as [20]

$$\tau = n \frac{C_{\text{gs}} + C_{\text{gd}}}{g_{m, \text{max}}} + R_L C_{\text{gd}} \left( 1 + n \frac{\langle g_m \rangle}{g_{m, \text{max}}} \right) \quad (1)$$

where  $C_{\text{gs}}$  is the gate-source capacitance,  $C_{\text{gd}}$  is the gate-drain capacitance,  $g_{m, \text{max}}$  is the maximum transconductance,  $\langle g_m \rangle$  is the average transconductance, and  $n$  is the number of load transistors for the current switch and source-follower circuit ( $n$  is one for the DTFF and two for the STFF). The  $\tau_{\text{CI}}$  can be regarded here as the time constant of discharge for a CI when the CI is initially charged to some signal level. Since the CI does not have a latching function, it has to hold some signal level with a time constant of  $\tau_{\text{CI}}$  in order to transfer the level to the other CI before the level vanishes by discharge. The DTFF, therefore, has some minimum value of  $R_L$  for toggle operation, whereas the STFF with a latching function does not have such a limitation. This discharging mechanism is considered to be the reason the DTFF needs a large  $R_L$ .

For a short-gate-length HEMT, such as the one used in this paper, the typical values of the  $C_{\text{gs}}$ ,  $C_{\text{gd}}$ ,  $g_{m, \text{max}}$ , and  $\langle g_m \rangle$  are  $0.7\text{ pF/mm}$ ,  $0.3\text{ pF/mm}$ ,  $1\text{ S/mm}$ , and  $0.75\text{ S/mm}$ , respectively. For the  $R_L$  used in the design and using (1), the  $\tau_{\text{CI}}$  and  $\tau_{\text{DL}}$  were calculated to be 4.4 and 3.7 ps, respectively. This larger  $\tau_{\text{CI}}$  than  $\tau_{\text{DL}}$  is an example of the larger  $\tau_{\text{CI}}$  due to the larger  $R_L$  in a CI than that in a D-latch originated from the level-holding mechanism described above. Using the relation expressed as [19]

$$f_{\text{tog max}} = \frac{1}{2\tau} \quad (2)$$

the ratio of  $f_{\text{tog max}}$  for the DTFF to that for the STFF is calculated to be 0.8. In contrast, the corresponding ratio obtained by circuit simulation is two (see Fig. 2). The discrepancy between these ratios suggests some speed-up mechanism of the DTFF which is not accounted for by linear-response theory. Possible mechanisms are the waveform-clip effect reported for the STFF [20] and the cross-point shift effect reported for the high-speed latching operation flip-flop (HLO-FF) [19].

In the design of high-speed digital circuits, delays caused by interconnections cannot be neglected. We, therefore, minimized the signal path length in order to reduce the signal transit delay through interconnection lines [21]. Due to the smaller scale of circuit for the CI than for the D-latch, the critical signal-path length for a CI was reduced from 450  $\mu\text{m}$  for a D-latch to 300  $\mu\text{m}$ . The output impedances of each

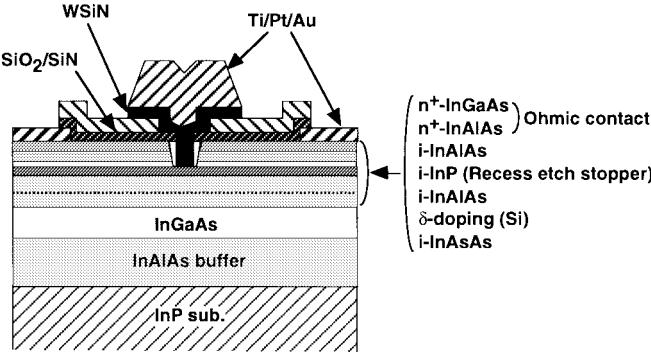

Fig. 3. Structure of an InAlAs/InGaAs/InP HEMT with a T-shaped gate, WSiN refractory gate metal, an  $\text{SiO}_2/\text{SiN}$  bilayer dielectric-film system, and InP recess-etch stopper.

stage of the CI's were matched as closely as possible to those of the interconnection lines by optimizing the gatewidth of the FET's [21]. Since the characteristic impedance of interconnection lines is approximately  $50 \Omega$ , the optimized gatewidth for the FET's in the DTFF and STFF was  $20 \mu\text{m}$ . The gatewidth for the input buffer was chosen to be  $50 \mu\text{m}$ , so as to give priority to driving capability, whereas that of the output buffer was chosen to be  $20 \mu\text{m}$ , in order to generate sufficient output amplitude and not to reduce the operation speed of the DTFF and STFF.

### III. PERFORMANCE

#### A. InAlAs/InGaAs/InP HEMT

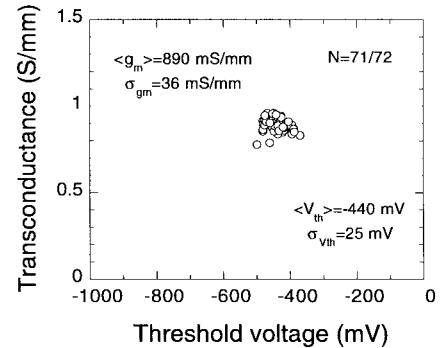

Fig. 3 shows a cross section of the HEMT, which has a gate length of  $0.1 \mu\text{m}$ . An InAlAs/InGaAs modulation-doped heterostructure lattice-matched to InP substrate was grown by metal-organic chemical vapor deposition (MOCVD). A direct EB writer was used to delineate the footprint of the T-shaped-gate electrode and conventional optical lithography was used to delineate the top part of it [22]. This fabrication process has high accuracy and reproducibility in the size of the gate electrode. WSiN was used as the Schottky-contact metal in order to improve the thermal hardness of the contact [23]. An  $\text{SiO}_2/\text{SiN}$  bilayer dielectric-film system [24] on the semiconductor surface was used to reduce the aspect ratio of the narrow groove for the gate footprint and to completely fill the groove with WSiN. To ensure the uniformity of the gate-recess depth, an InP layer was inserted into the InAlAs barrier layer as a gate-recess-etch stopper [22]. Fig. 4 shows the distribution of threshold voltage ( $V_{\text{th}}$ ) and transconductance ( $g_m$ ) for the HEMT's on a 2-in wafer on which the frequency dividers were fabricated. The use of the InP recess-etch stopper resulted in the standard deviation ( $\sigma$ ) of  $V_{\text{th}}$  being only  $25 \text{ mV}$ . The  $g_m$  of these HEMT's was  $890 \pm 36 \text{ mS/mm}$  (mean  $\pm \sigma$ ). The current-gain cutoff frequency ( $f_T$ ) of the HEMT's was high and uniform:  $164 \pm 7.6 \text{ GHz}$ . Seventy-one of the 72 FET's on the wafer worked well.

#### B. IC Performance

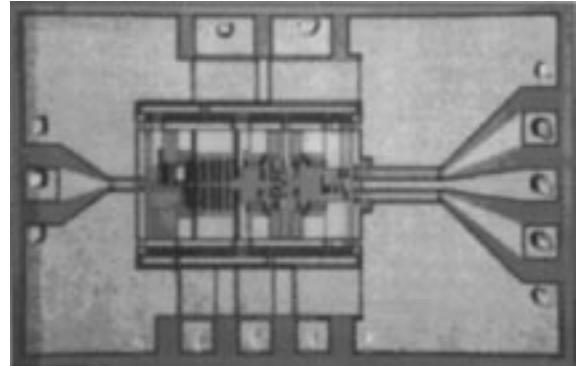

The frequency dividers described in Section II were fabricated using the InAlAs/InGaAs/InP HEMT's described above. Fig. 5 is a photomicrograph of the SCFL DFD, whose chip

Fig. 4. Transconductance ( $g_m$ ) versus threshold voltage ( $V_{\text{th}}$ ) for  $0.1\text{-}\mu\text{m}$ -gate HEMT's on a 2-in wafer.

Fig. 5. Photomicrograph of a DFD using  $0.1\text{-}\mu\text{m}$  InAlAs/InGaAs/InP HEMT's.

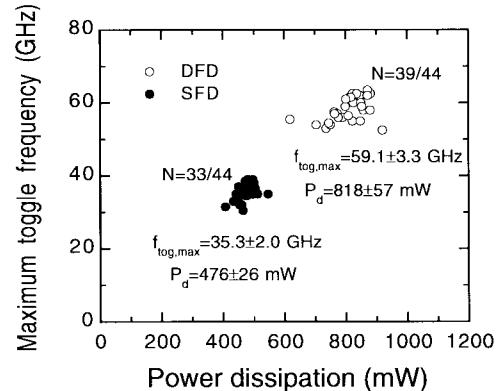

Fig. 6. Distribution of maximum toggle frequency ( $f_{\text{tog},\text{max}}$ ) and power dissipation ( $P_d$ ) of the DFD's and SFD's on a 2-in wafer. (DFD:  $V_{ss} = -4.6 \text{ V}$ ,  $V_{cs} = 0.60 \text{ V}$ ,  $V_{\text{ref}} = -2.58 \text{ V}$ . SFD:  $V_{ss} = -3.2 \text{ V}$ ,  $V_{cs} = 0.70 \text{ V}$ ,  $V_{\text{ref}} = -2.20 \text{ V}$ ).

size is  $1.4 \times 0.9 \text{ mm}$ . The IC has Schottky diodes for level shifting, metal-insulator-metal (MIM) capacitors with SiN as a dielectric film, and resistors using active layers. The interconnection lines are one-layer metal and air-bridge crossovers which were originally developed for MMIC's. Fig. 6 shows the distribution of  $f_{\text{tog},\text{max}}$  and the power dissipation ( $P_d$ ) of DFD's and SFD's on the same 2-in wafer. The biases were optimized for high-speed operation. For 44 samples, the fabrication yields of DFD's and SFD's were as high as 89% and 75%. The  $f_{\text{tog},\text{max}}$  values were high and uniform:  $59.1 \pm 3.3 \text{ GHz}$  for DFD's and  $35.3 \pm 2.0 \text{ GHz}$  for SFD's, and the respective  $P_d$  values were  $818 \pm 57$  and  $476 \pm 26 \text{ mW}$ . The

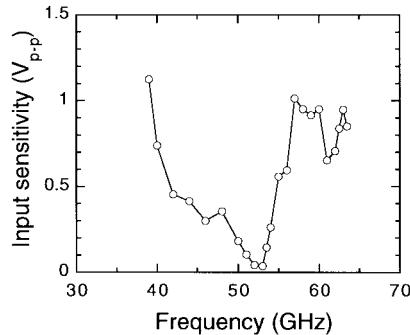

Fig. 7. Input sensitivity versus frequency for a DFD. The frequency of self-oscillation is 52.5 GHz. The ripples are due to residual reflection in the measurement system. ( $V_{ss} = -4.6$  V,  $V_{cs} = 0.58$  V,  $V_{ref} = -2.58$  V,  $I_{ss} = 181$  mA,  $I_{cs} = 11$  mA,  $I_{ref} = 0$  mA).

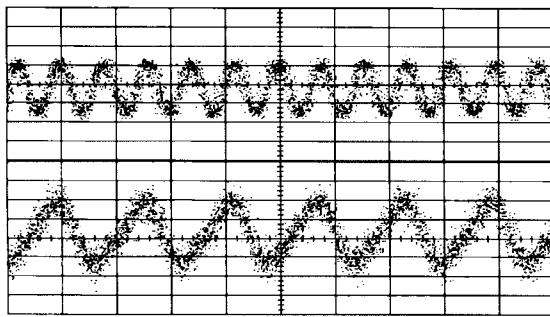

Fig. 8. Input and output waveforms of a DFD. The input (upper) and the output (lower) frequencies are 63.5 and 31.75 GHz, respectively, and their amplitudes are 850 and 140 mV. ( $V_{ss} = -4.6$  V,  $V_{cs} = 0.58$  V,  $V_{ref} = -2.58$  V,  $I_{ss} = 181$  mA,  $I_{cs} = 11$  mA,  $I_{ref} = 0$  mA).

higher  $P_d$  of the DFD is due to the lower optimum  $V_{ss}$ , which is naturally caused by the lower center level of logic swing ( $V_{CL}$ ) at the output of the current switch, which, in turn, is due to the larger  $R_L$ . In fact, the calculated  $V_{CL}$  difference of 1.4 V for a typical saturation current of 0.7 A/mm agrees well with the measured optimum  $V_{ss}$  difference between the DFD and the SFD. Fig. 7 shows input sensitivity for one of the DFD's, which showed stable toggle operation up to 63.5 GHz. The operation bandwidth, without tuning, is as broad as 24.5 GHz. Fig. 8 shows input and output waveforms of the frequency divider operating at 63.5 GHz. To our knowledge, this operation frequency is the highest ever reported for a digital frequency divider. It is also the highest clock frequency reported for a digital IC synchronized to a clock signal.

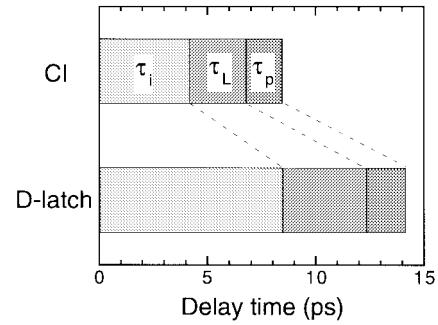

### C. Delay-Time Analysis

Delay-time analysis was carried out for the CI in the DFD and the D-latch in the SFD (see Fig. 9). The total delay time ( $\tau$ ) for the CI and the D-latch were calculated from the measured average  $f_{\text{tog},\text{max}}$  in Fig. 6 and proven to be 8.5 and 14.2 ps. The intrinsic circuit delay ( $\tau_i$ ) was evaluated from circuit simulations neglecting the parasitic effect caused by interconnection lines and the stray capacitance. The  $\tau_i$  values calculated for the CI and the D-latch were 4.2 and 8.5 ps, respectively. The signal transit delay ( $\tau_L$ ) through interconnection lines were evaluated (using  $LC$  line approximation) as  $\tau_L = L/v_s$ , where the  $L$  is the length of an interconnection line and the  $v_s$  is the signal-propagation

Fig. 9. Delay-time analysis of the CI and the D-latch.  $\tau_i$  is the intrinsic circuit delay,  $\tau_L$  is the interconnection-line delay, and  $\tau_p$  is the parasitic charging delay.

velocity on the line [22]. Note that this  $LC$  line approximation is valid for interconnection lines used in our design when the frequency is higher than 2 GHz. For the signal-path length, described in Section II, the  $\tau_L$  values for the CI and the D-latch were calculated to be 2.6 and 3.9 ps, respectively. The  $\tau_p$  is the remaining delay calculated from the relation  $\tau_p = \tau - \tau_i - \tau_L$ , which can be interpreted as the charging delay of stray capacitance. This delay was 1.7 ps for the CI and 1.8 ps for the D-latch. Eliminating the latch function and optimizing pattern layouts decreased the  $\tau$ ,  $\tau_i$ ,  $\tau_L$ , and  $\tau_p$  values for the CI to be 60%, 49%, 67%, and 94% of the corresponding delays for the D-latch. Consequently, the decrease of the  $\tau$  is due not only to the decrease of the  $\tau_i$ , but also to the decrease of the  $\tau_L$ . However, the decrease of  $\tau_L$  is smaller than that of  $\tau_i$ , and the decrease of  $\tau_p$  is small. Therefore, the  $\tau$  decrease due to using the CI becomes smaller and the  $\tau$  for the CI remains 60%, as much as the  $\tau$  for the D-latch, even though the  $\tau_i$  decreased to 49%. In addition, the ratios of  $\tau_L$  and  $\tau_p$  to  $\tau$  increase from 27% and 13% to 31% and 20%, respectively. This shows that the reduction of  $\tau_L$  and  $\tau_p$  is of more importance in increasing the speed of the DTFF than in increasing the speed of the STFF. The large  $\tau_L$  is due to the interconnection-line process developed for MMIC's, where the width and space of air-bridges is too large for digital IC's. Accordingly, the optimization of an interconnection-line process is necessary. Decreasing stray capacitance is also necessary because doing so will increase the overall speed of the DTFF.

### IV. CONCLUSION

Digital DFD's employing a DTFF with SCFL CI's and SFD's employing a STFF with SCFL D-latches were fabricated using 0.1- $\mu$ m InAlAs/InGaAs/InP HEMT's of good uniformity and high performance. They showed excellent yield and uniformity: fabrication yields of 89% and 75% on a 2-in wafer, and  $f_{\text{tog},\text{max}}$  values of  $59.1 \pm 3.3$  and  $35.3 \pm 2.0$  GHz. A DFD achieved a record broad-band toggle operation at 39–63.5 GHz without tuning. Comparison of the DFD and the SFD showed that the ratio of  $f_{\text{tog},\text{max}}$  for the DFD to that for the SFD by circuit simulation is much higher than the expected value using linear-response theory, which shows the existence of some effects that increases the operation speed of the DFD. The comparison also showed that the measured ratio of the  $f_{\text{tog},\text{max}}$  for the DFD to that for the SFD is 1.7, in contrast with the value of two predicted from the circuit simulation.

Delay-time analysis using an *LC* line approximation revealed that this 15% decrease of the ratio is due to the transit delay of interconnections and charging delay for stray capacitance. Reduction of these parasitic delays is, therefore, important for further increasing the operation speed. The fabricated IC showed the highest operation speed of any digital frequency divider and demonstrated that this technology can be used to make digital IC's that can operate at more than 60 Gb/s. The next step to speed-up this type of digital IC is to use fine bilayer interconnection system to shorten the interconnection length. In addition, the use of thick low-permittivity dielectric film like benzocyclobutene (BCB) is effective in decreasing interconnection delay because it increases the propagation speed of a signal. As a result, 80-Gb/s operation of a digital IC will be possible by using these high-speed interconnections.

#### ACKNOWLEDGMENT

The authors would like to thank K. Murata, T. Otsuji, Y. Imai, and E. Sano for their useful discussions on circuits. Special thanks go to T. Kusumoto and T. Maruyama for their help in the fabrication process, and to K. Nishihata for his help in the measurement.

#### REFERENCES

- [1] L. D. Nguyen, A. S. Brown, M. A. Thompson, and L. M. Jelloian, "50-nm self-aligned gate pseudomorphic AlInAs/GaInAs high electron mobility transistors," *IEEE Trans. Electron Devices*, vol. 39, pp. 2007-2014, Sept. 1992.

- [2] P. M. Smith, S. M. J. Jiu, M. Y. Kao, P. Ho, S. C. Wang, K. H. G. Duh, S. T. Fu, and P. C. Chao, "W-band high efficiency InP-based power HEMT with 600 GHz  $f_{max}$ ," *IEEE Microwave Guided Wave Lett.*, vol. 5, pp. 230-232, July 1995.

- [3] M.-Y. Kao, K.-H. G. Duh, P. Ho, and P.-C. Chao, "An extremely low-noise InP-based HEMT with silicon nitride passivation," in *IEEE Int. Electron Devices Meeting*, San Francisco, CA, Dec. 1994, pp. 907-910.

- [4] R. T. Webster, J. Slobodnik, and G. A. Roberts, "Monolithic InP HEMT V-band low-noise amplifier," *IEEE Microwave Guided Wave Lett.*, vol. 2, pp. 236-238, June 1992.

- [5] Y. Umeda, T. Enoki, K. Arai, and Y. Ishii, "High-performance InAlAs/InGaAs HEMT's and their application to a 40-GHz monolithic amplifier," in *Extended Abstracts Int. Conf. Solid-State Devices Materials*, Tsukuba, Japan, Aug. 1992, pp. 573-575.

- [6] A. Kurdoghlian, W. Lam, C. Chou, L. Jellian, A. Igawa, M. Matloubian, L. Larson, A. Brown, M. Thompson, and C. Ngo, "High-efficiency InP-based HEMT MMIC power amplifier," in *IEEE GaAs IC Symp. Dig.*, San Jose, CA, Oct. 1993, pp. 375-377.

- [7] R. Majidy-Ahy, C. K. Nishimoto, M. Riaziat, M. Glenn, S. Silvermann, S.-L. Weng, Y.-C. Pao, G. A. Zudasiuk, S. G. Bandy, and Z. C. H. Tan, "5-100 GHz InP coplanar waveguide MMIC distributed amplifier," *IEEE Trans. Microwave Theory Tech.*, vol. 38, Dec. 1990.

- [8] Y. Kwon, D. Pavlidis, M. Tutt, G. I. Ng, and T. Brock, "W-band monolithic mixer using InAlAs/InGaAs HEMT," in *IEEE GaAs IC Symp. Tech. Dig.*, New Orleans, LA, Oct. 1990, pp. 181-184.

- [9] Y. Kwon, D. Pavlidis, M. Tutt, G. I. Ng, R. Lai, and T. Brock, "W-band monolithic oscillator using InAlAs/InGaAs HEMT," *Electron. Lett.*, vol. 26, no. 18, pp. 1425-1426, Aug. 1990.

- [10] K. W. Chang, H. Wang, R. Lai, D. C. Lo, and J. Berenz, "A V-band monolithic InP HEMT downconverter," in *IEEE GaAs IC Symp. Dig.*, San Jose, CA, Oct. 1993, pp. 211-214.

- [11] U. K. Mishra, J. F. Jensen, A. S. Brown, M. A. Thompson, L. M. Jelloian, and R. S. Beaubien, "Ultra-high-speed digital circuit performance in 0.2- $\mu$ m gate-length AlInAs/GaInAs HEMT technology," *IEEE Electron Device Lett.*, vol. 9, pp. 482-484, Sept. 1988.

- [12] T. Takada, K. Osafune, M. Iida, and N. Ohta, "GaAs high speed decision circuit," IECE, Japan, Tech. Rep. SSD82-111, pp. 43-48, 1983 (in Japanese).

- [13] T. Enoki, Y. Umeda, K. Osafune, H. Ito, and Y. Ishii, "Ultrahigh-speed InAlAs/InGaAs HEMT's IC's using pn-level-shift diodes," in *Proc. IEDM Tech. Dig.*, Washington, DC, Dec. 1995, pp. 193-196.

- [14] T. Otsuji, M. Yoneyama, Y. Imai, S. Yamaguchi, T. Enoki, Y. Umeda, and E. Sano, "46 Gbit/s multiplexer and 40 Gbit/s demultiplexer IC modules using InAlAs/InGaAs/InP HEMT's," *Electron. Lett.*, vol. 32, no. 7, pp. 685-686, 1996.

- [15] J.-C. Sarkissian, M. Camiade, P. Savary, A. Suares, R. Quere, and J. Obregon, "A 60-GHz HEMT-MMIC analog frequency divider by two," *IEEE J. Solid-State Circuits*, vol. 30, pp. 1062-1067, Oct. 1995.

- [16] C. J. Madden, D. R. Snook, R. L. V. Tuyt, M. V. Le, and L. D. Nguyen, "A novel 75 GHz InP HEMT dynamic divider," in *IEEE GaAs IC Symp. Dig.*, Orlando, FL, Oct. 1996, pp. 137-140.

- [17] A. Thiede, M. Berroth, P. Tasker, M. Schlechtweg, J. Seibel, B. Raynor, A. Hulsmann, K. Kohler, and W. Bronner, "Digital dynamic frequency dividers for broad-band application up to 60 GHz," in *IEEE GaAs IC Symp. Dig.*, San Jose, CA, Oct. 1993, pp. 91-94.

- [18] Y. Matsuoka, S. Yamahata, S. Yamaguchi, K. Murata, E. Sano, and T. Ishibashi, "IC-oriented self-aligned high-performance AlGaAs/GaAs ballistic collection transistors and their applications to high-speed IC's," *IEICE Trans. Electron.*, vol. E76-C, no. 9, pp. 1392-1401, Sept. 1993.

- [19] K. Murata, T. Otsuji, E. Sano, M. Ohhata, M. Togashi, and M. Suzuki, "A novel high-speed latching operation flip-flop (HLO-FF) circuit and its application to a 19-Gb/s decision circuit using a 0.2- $\mu$ m GaAs MESFET," *IEEE J. Solid State Circuits*, vol. 30, pp. 1101-1108, Oct. 1995.

- [20] Y. Umeda, T. Enoki, K. Osafune, H. Ito, and Y. Ishii, "High-yield design technologies for InAlAs/InGaAs/InP-HEMT analog-digital IC's," *IEEE Trans. Microwave Theory Tech.*, vol. 44, pp. 2361-2368, Dec. 1996.

- [21] Y. Umeda, K. Osafune, T. Enoki, H. Ito, and Y. Ishii, "SCFL static frequency divider using InAlAs/InGaAs/InP HEMT's," in *Proc. 25th European Microwave Conf.*, Bologna, Italy, Sept. 1995, pp. 222-228.

- [22] T. Enoki, T. Kobayashi, and Y. Ishii, "Device technologies for InP-based HEMT's and their application to IC's," in *IEEE GaAs IC Symp. Tech. Dig.*, Philadelphia, PA, Oct. 1994, pp. 337-340.

- [23] T. Enoki, H. Ito, and Y. Ishii, "Reliability study on InAlAs/InGaAs HEMT's with an InP recess etch stopper and refractory gate metal," *Solid State Electron.*, vol. 41, no. 10, pp. 1651-1656, 1997.

- [24] T. Enoki, M. Tomizawa, Y. Umeda, and Y. Ishii, "0.05- $\mu$ m-gate InAlAs/InGaAs high electron mobility transistor and reduction of its short-channel effects," *Jpn. J. Appl. Phys. I, Regul. Rap. Short Notes*, vol. 33, no. 1B, pp. 798-803, Jan. 1994.

**Yohtaro Umeda** (M'89) was born in Kanagawa, Japan, on September 1, 1957. He received the B.S. and M.S. degrees in physics from the University of Tokyo, Tokyo, Japan, in 1982 and 1984, respectively.

In 1984, he joined Nippon Telegraph and Telephone (NTT) Corporation. He is currently with NTT System Electronics Laboratories, Kanagawa, Japan, where he is engaged in the study of microwave characteristics of HEMT's on InP and its application to monolithic millimeter-wave IC's and ultrahigh-speed digital IC's.

Mr. Umeda is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.

**Kazuo Osafune** (M'75) was born in Tokyo, Japan, on April 20, 1948. He received the B.S., M.S., and Ph.D. degrees in electronic engineering from the University of Tokyo, Tokyo, Japan, in 1972, 1974, and 1990, respectively.

In 1979, he joined the Yokosuka Electrical Communication Laboratory, Nippon Telegraph and Telephone (NTT) Public Corporation, Kanagawa, Japan, where he has been engaged in the research of optical, coaxial cable, and millimeter-waveguide transmission systems. Since 1983, he has been with the NTT Systems Electronics Laboratories, Atsugi-shi, Japan, where he has been engaged in the research and development of the design of high-speed and high-frequency GaAs, InP, and Si IC's.

Dr. Osafune is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan, and the Japan Society of Applied Physics.

**Takatomu Enoki** (M'91) was born in Tottori, Japan, on November 19, 1959. He received the B.S. and M.S. degrees in physics and the Ph.D. degree in electronic and electrical engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 1982, 1984, and 1996, respectively.

In 1984, he joined the Atsugi Electrical Communications Laboratories, Nippon Telegraph and Telephone (NTT) Public Corporation, Kanagawa, Japan, where he has been engaged in research and development on fabrication technologies for high-frequency and high-speed GaAs MESFET's and IC's. Since 1989, he has studied and developed ultrahigh speed and low-noise heterojunction FET's and their IC's on InP substrates. He is currently a Senior Manager in the Research Planning Department, NTT System Electronics Laboratories, Kanagawa, Japan.

Dr. Enoki is a member of the Institute of Electronics, Information, and Communication Engineers (IEICE), Japan, and the Japan Society of Applied Physics.

**Haruki Yokoyama** was born in Kochi, Japan, on March 7, 1965. He received the B.S. and M.S. degrees in electrical engineering from Hiroshima University, Hiroshima, Japan, in 1987 and 1989, respectively, and the Ph.D. degree in applied physics from Tohoku University, Sendai, Japan, in 1996.

In 1989, he joined the Nippon Telegraph and Telephone (NTT) LSI Laboratories (now NTT System Electronics Laboratories), Kanagawa, Japan. Since then, he has been engaged in research and development on the epitaxial growth technologies of III-V compound semiconductors. Since 1995, he has studied and developed the InP-based material growth using MOVPE to fabricate ultrahigh speed and low-noise heterojunction FET's.

Dr. Yokoyama is a member of the Japan Society of Applied Physics.

**Yasunobu Ishii** (M'90) received the B.S., M.S., and Ph.D. degrees in electronic engineering from Osaka University, Osaka, Japan, in 1973, 1975, and 1984, respectively.

In 1975, he joined the Electrical Communication Laboratories, Nippon Telegraph and Telephone (NTT) Public Corporation, Tokyo, Japan, where he has been engaged in research on GaAs MESFET's. He is currently with NTT System Electronics Laboratories, Kanagawa, Japan, working as an Executive Research Engineer and Research Group Leader in

charge of the research and development of advanced heterostructure electron devices based on InP.

Dr. Ishii is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan, and the Japan Society of Applied Physics.

**Yoshihiro Imamura** was born in Shiga-Pref., Japan, on January 25, 1945. He received the B.E. and M.E. degrees in metallurgy from Kyoto University, Kyoto, Japan, in 1968 and 1970, respectively, and the Dr.Eng. degree from Osaka University, Osaka, Japan, in 1980.

In 1970, he joined Musashino Laboratories, Nippon Telegraph and Telephone (NTT) Public Corporation, Tokyo, Japan, where he began research work on magnetic memory materials. In 1977, he joined the Material Science Department, Massachusetts (MIT), Cambridge. Upon his return to NTT, he was mainly engaged in III-V semiconductor crystal growth for high-speed electronic devices and for optical devices. He was a Manager of the R&D Department, NTT, for InP-based laser diode and ultrahigh speed electronic device for several years, prior to his joining the Corning Shizuoka Technical Center, Corning Company Ltd., Sizuoka, Japan, in October 1997, where he is currently the Manager for photonic components.

Dr. Imamura is a member of the Japanese Applied Physical Society.